2.4.2000 Neues vom LGP-30

("Nr. 4 lebt")

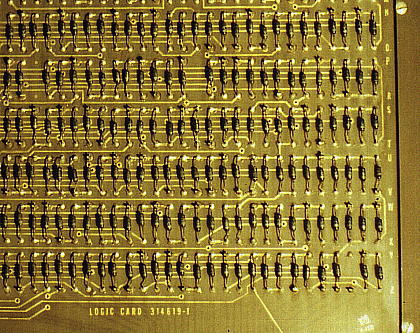

Logik-Platine und Netzliste

Eine kleine Anmerkung vorweg: Inzwischen haben wir nach zweimaligem Durchmessen aller Dioden auf der originalen Logik-Platine die defekte Diode gefunden, die für das Fehlverhalten des Y- und des R- Befehls verantwortlich war.

Ansonsten haben wir eine praktisch komplette Netzliste aller Verbindungen der einzelnen Module des Rechners untereinander aufgestellt, die Schaltpläne aller Module gezeichnet (mit Ausnahme der beiden Module in der Oszilloskopeinheit). Außerdem kennen wir alle 140 Anschlüsse des Logikboards, sowie die Dioden, die eine Verbindung nach außen haben und circa die Hälfte der Verbindungen der Dioden untereinander.

Zum Thema Schaltplan: Ein Gesamtschaltplan des Rechners wäre zwar eine imponierende Fleißarbeit, mit der man einen Raum tapezieren könnte, er wäre wegen seiner Unübersichtlichkeit aber kaum praktisch zu gebrauchen. Wir haben uns deshalb auf Netzlisten beschränkt, die stärker abstrahieren und zudem den Vorteil haben, als ASCII-Dateien mit einem Texteditor durchsucht werden zu können. Wo es für das Verständnis sinnvoll ist, kann man immer noch einen Teilschaltplan herauszeichnen.

Ein Ausschnitt der Logik-Platine

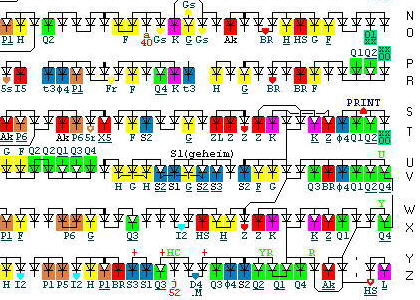

Darunter der gleiche Ausschnitt

(Dioden N33 .. Y60) in einer etwas abstrahierteren Form.

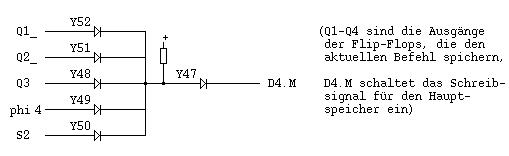

Aus dem bunten Bild erkennt der Kenner beispielsweise sofort: Die Dioden Y48 bis Y52 (alle Dioden sind immer mit den Koordinaten ihrer Anoden bezeichnet) bilden ein UND-Gatter und dekodieren die beiden Befehle Y (Adressenersatz) und R (Rückkehradresse) während Phase 4, der Befehlsaus- führungsphase:

Die Unterscheidung der beiden Befehle untereinander geschieht dann über W60, W59, Y56 und Y57, die, wenn Q4_ = 1 ist, den Akkuinhalt an den Eingang des Hauptspeicherschreibverstärkers anlegt, bzw. über Y53 und Y54, die wenn Q4 = 1 ist, den Ausgang des Adreßincrementers an den Eingang des Schreibverstärkers anlegt. Aktiv wird der Schreibverstärker allerdings nur in Phase 4 und dann wegen S2 nur in der Zeit, in der der Adreßteil des Befehls vorliegt.