PDP-8/L I/O-Box

In der Euphorie über die gelungene Reparatur des PDP-8/L im vergangenen Jahr habe ich mit dem Bau einer Ein-Ausgabeerweiterung für die Maschine begonnen. Sie ist inzwischen praktisch fertig und bietet folgende Features:

- Zwei V24-Schnittstellen (9600 Bd)

- Zwei parallele Ausgabeschnittstellen mit je 12 Bit

- Zwei parallele Eingabeschnittstellen mit je 12 Bit

- Ein Timer

- Zwei IRQ-Eingänge z. b. V.

Im Moment steuere ich mit den parallelen Ports die IBM 73 Kugelkopfschreib- maschine an, die dadurch zum Schönschreibdrucker wird.

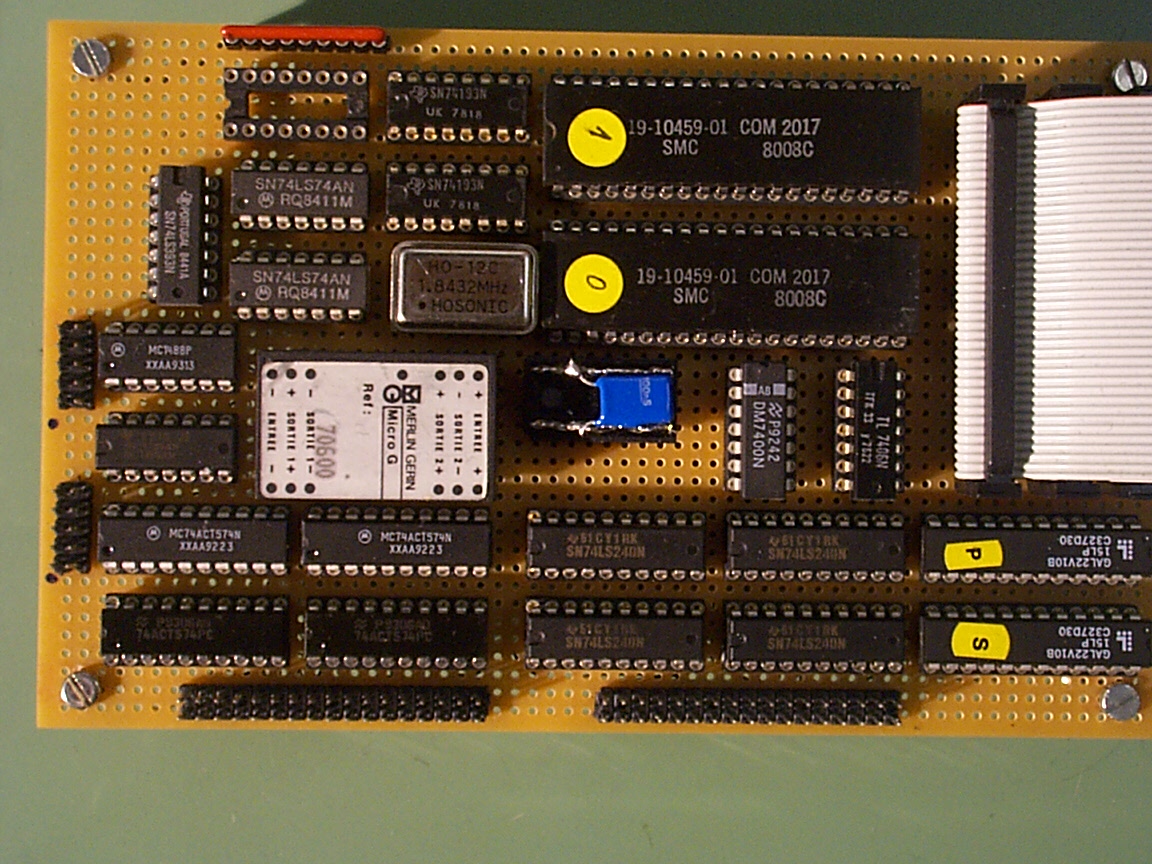

Die Platine in der Box

Dieses ist die Logikplatine der I/O-Box. Einige der Bauteile auf dem Photo können zur Erklärung angeklickt werden.

Die beiden UARTs

UART bedeutet: Universal Asynchronous Receiver/Transmitter

Zwei altertümliche UARTs in PMOS-Technologie. Sie benötigen zwei

Betriebsspannungen, Vcc = +5V und Vdd = -12V, die durch den DC-DC-Wandler

auf der Platine erzeugt wird.

Beide UARTs werden hier mit einer Baudrate von 9600 Bd betrieben.

DC-DC-Wandler

Erzeugt aus der 5V-Betriebsspannung jeweils +12V und -12V. Die -12V werden für die UARTS in PMOS-Technologie und für die V24-Treiber, die +12V nur für die V24-Treiber benötigt.

Positiver I/O-Bus

Der Anschluß der IO-Box erfolgt über drei 40-polige Flachbandkabel. Auf

dem Bild ist nur das oberste zu sehen.

Der Ausdruck positiver I/O-Bus zeigt den Gegensatz zum 'classic' PDP-8,

der mit diskreten PNP-Germanium-Transistoren aufgebaut ist, und mit

negativer Betriebsspannung arbeitet.

Da viele Peripheriegeräte jeweils von der vorhergehenden Rechnergeneration

übernommen wurden, gab es Pegelanpaßschaltungen zwischen den verschiedenen

Bussen.

Zwei GALs

Diese beiden GALs sind der Sündenfall auf der Platine: Sie sind viel zu modern und ersetzen 20 bis 30 SSI-TTL-Chips, die sonst die sogenannte 'Glue-Logik' gebildet hätten. Sie besorgen im wesentlichen die Dekodierung der Befehle und Adressen auf dem PDP-8-Bus, und erzeugen die Signale, mit denen die diversen Puffer, Latches und Flip-Flops gesteuert werden.

Parallel-Ports

An diese beiden Pfostensteckern sind die vier 12-Bit Parallelports

angeschlossen: Zwei Input-Ports, zwei Output-Ports.

Die Output-Ports sind nach dem Einschalten oder dem Anhalten der Maschine

hochohmig, so daß daran angeschlossene Relais oder Transistoren nicht

angesteuert werden.

Die Ports besitzen TTL-Pegel, wobei die Ausgänge genügend Treiberleistung

besitzen, um direkt kleine Relais ansteuern zu können.

Input Buffer

Wer ein TTL-Datenbuch besitzt, kann feststellen, dass die hier verwendeten

Puffer invertieren. Das liegt daran, dass der AC-(Eingabebus) des PDP-8/L

mit negativer Logik arbeitet: 0 = +5V, 1 = 0V.

Um Bezeichnungskonfusionen vorzubeugen: Der 'positive I/O-Bus' hat

seinen Namen von der verwendeten positiven Spannung, er arbeitet aber

trotzdem mit negativer Logik.

Zur Zeit der Konstruktion des 8/L gab es noch keine Tristate-Logik.

Busse, an denen es mehrere Datenquellen gab, wurden daher mit

Open-Kollektorbausteinen realisiert.

Alle IC-Ausgänge oder Transistoren arbeiten auf einen gemeinsamen

Kollektorwiderstand. Sind alle Ausgänge gesperrt, zieht der Widerstand

den Bus nach +5V, was als logisch 0 interpretiert wird. Leitet einer der

Ausgänge, dann wird der Bus nach 0V gezogen, was als logisch 1

interpretiert wird. Es können auch mehrere Ausgänge gleichzeitig leiten,

es wird das logische Oder ('wired OR') gebildet.

Nach der Einführung der Tristate-Logik gab es als Übergang zu den

existierenden O.C.-Bussen daher eine Zeit lang invertierende

Tristate-Treiber wie den hier verwendeten 74LS240.

Dabei ist aber Vorsicht geboten. Im Gegensatz zu O.C.-Treibern dürfen

bei Tristate-Treibern nicht zwei Treiber zugleich aktiv sein, sonst

entsteht Wärme.

Viele PDP-8 Befehle beruhen übrigens auf praktischer

Anwendung des wired OR:

Der Befehl OSR 'verODERrt' den Inhalt des Akkumulators mit dem des

Switchregisters per wired OR.